Software-Defined Radio

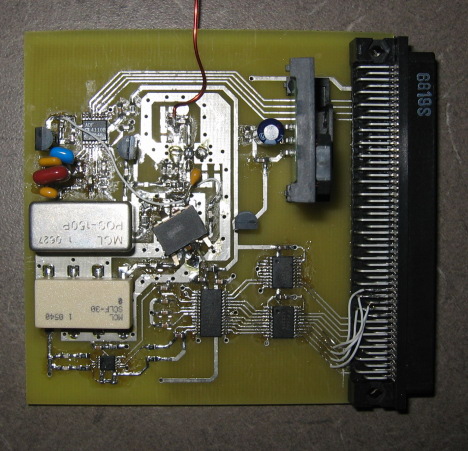

This board downconverts and digitizes the FM broadcast band. It connects to the Digilent S3E-1600 board which selects a channel and sends the IF over Ethernet to a computer which demodulates the audio.

The sample clock is produced by a CY22150 clock synthesizer connected to J4 on the S3E-1600 board.

The local oscillator is generated by an ADF4110 PLL.

Channel selection is performed by a 256-point FFT (generated with Xilinx's Core Generator). A narrow channel bandwidth is achieved with a WOLA (Weighted OverLap and Add) filter which is equivalent to using a larger, windowed FFT and discarding the unused FFT outputs.

IF data is sent to the host over ethernet using a stripped-down version of the Ethernet core from opencores.org. The UDP packet header is hard-coded in the FPGA.

Assembled Board